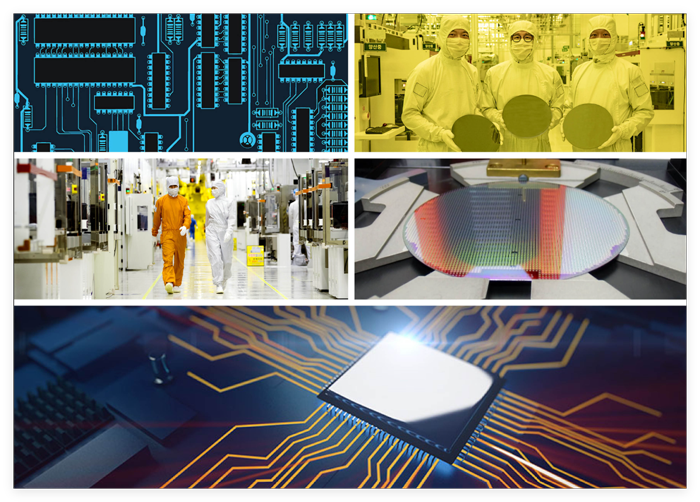

半导体产业关键环节计算特点分析、算法、软件工具,其高速计算设备硬件配置推荐

半导体产业是一个极其复杂且高度专业化的全球性产业链。其关键环节可分三个主要部分:设计(Design)、制造(Manufacturing)和封装测试(Assembly, Testing, and Packaging, ATP)。

以下是对每个部分的主要功能、核心算法、软件工具以及推荐硬件配置的详细分解。

1. 半导体/IC设计

这一阶段专注于芯片的规格制定、逻辑设计、物理实现和验证,如同绘制建筑蓝图。

(1) 主要功能:

- 规格定义:确定芯片的功能、性能、功耗、面积等目标。

- 架构设计:设计芯片的宏观结构,如CPU的核数、缓存大小等。

- 前端设计:

a)RTL设计:使用硬件描述语言(如Verilog, VHDL)编写代码,描述电路的逻辑功能。

b)功能验证:通过仿真(Simulation)和形式验证(Formal Verification)确保RTL代码的功能符合规格。

c)逻辑综合:将RTL代码转换为逻辑门(与、或、非等)组成的网表。

- 后端设计:

d)物理设计:将网表转化为实际的物理版图,包括布局、布线。

e)时序分析/签核:确保芯片在目标频率下能正常工作,没有时序违例。

f)物理验证:检查版图是否符合制造规则(DRC)、电气规则(LVS)等。

(2) 主要软件工具(EDA-电子设计自动化)

市场主要由三大巨头(“EDA三巨头”)主导:

- Synopsys (新思科技): VCS(仿真),Design Compiler(逻辑综合-行业标准),PrimeTime(时序签核-行业标准),ICC2(布局布线)。

- Cadence (楷登电子): Xcelium(仿真),Genus(逻辑综合),Innovus(布局布线),Virtuoso(模拟/版图设计-行业标准)。

- Siemens EDA (西门子-原Mentor Graphics):Questa(仿真),Calibre(物理验证-行业标准)。

- 其他:Ansys(多物理场仿真,用于信号完整性、电源完整性分析)。

(3)主要算法:

- 逻辑仿真算法:事件驱动仿真(Event-driven simulation) 是核心。

- 时序分析算法:静态时序分析(Static Timing Analysis, STA) 算法,用于检查电路中的信号延迟是否满足时钟周期要求。

- 布局布线算法:高度复杂的组合优化算法,如模拟退火 (Simulated Annealing)、分区算法 (Partitioning) 来最小化走线长度和时延。

- AI与机器学习(ML):近年来的大趋势。AI被用于探索巨大的设计空间,自动优化PPA(功耗、性能、面积),加速验证收敛,以及预测布线拥塞。

(4)硬件配置推荐(EDA工作站/服务器):

EDA工作负载通常是“CPU 密集型”和“内存密集型”。

操作系统:Linux(几乎是绝对标准),特别是 Red Hat Enterprise Linux (RHEL) 或其兼容版本 (如 CentOS, Rocky Linux)。

CPU:高主频、多核心的处理器。

工作站:Intel Core i9/AMD Ryzen 9(用于单线程任务)。

服务器 (用于大型仿真/综合):AMD EPYC或Intel Xeon Gold/Platinum(核心数越多,并行处理能力越强)。

内存 (RAM):极其关键。

最低:32 GB。

推荐:64GB到128GB(用于中型设计)。

大型设计/仿真服务器:256GB到1TB或更多。

存储 (Storage):高速 NVMe SSD。

设计数据库(PDK, GDSII文件)和仿真波形文件都非常庞大(可达 TB 级),高速I/O是必需的。推荐1TB以上的PCIe 4.0/5.0 NVMe SSD。

GPU:传统上不重要,但现在越来越重要。

NVIDIA GPU(如RTX A系列, H100)正被用于加速特定任务,如AI驱动的设计、SPICE 仿真(如 Synopsys PrimeSim)和计算光刻(OPC)。

2. 半导体/ 晶圆制造

这一阶段是将设计好的蓝图在晶圆厂(Fab)中通过百道工序精确地复刻到硅晶圆上。

(1)主要功能:

- 晶圆制造:将硅锭 (Ingot) 切割、抛光成薄薄的晶圆 (Wafer)。

- 核心工艺:在晶圆上重复执行数百个步骤,主要包括:

- 光刻 (Photolithography):使用光(DUV 或 EUV)将电路图案从掩膜版 (Mask) 转移到晶圆的光刻胶上。

- 刻蚀 (Etch):去除没有被光刻胶保护的材料。

- 薄膜沉积 (Deposition):沉积薄层材料(导体或绝缘体)。

- 离子注入 (Ion Implantation):掺杂特定离子以改变硅的导电特性。

- 过程控制 (Process Control):在制造过程中实时监控和测量,确保每一步都精确无误。

- 良率管理 (Yield Management):分析缺陷数据,优化工艺参数,以最大限度地提高合格芯片的比例。

(2)主要软件工具:

- 制造执行系统 (MES):晶圆厂的“大脑”,用于跟踪和管理生产线上的每一片晶圆。例如Siemens Opcenter、Applied Materials的MES解决方案。

- 良率管理系统 (YMS):专门用于收集、分析所有测试和测量数据,以提高良率的软件。

- 统计过程控制 (SPC) 软件:监控工艺参数是否在控制范围内。

- 设备自动化软件 (CIM-计算机集成制造):控制和协调所有自动化生产设备(如光刻机、刻蚀机)。

(3)主要算法:

a)AI与机器学习(ML):在制造中处于核心地位。

- 计算机视觉 (CV):使用 CNN 等算法对晶圆进行自动光学检测 (AOI),识别微小的物理缺陷。

- 异常检测 (Anomaly Detection): 分析来自设备的传感器数据,实时发现工艺偏差。

- 预测性维护 (PdM):通过分析设备数据,预测设备何时可能发生故障,提前进行维护,避免生产中断。

b)排程与调度算法:复杂的运筹学算法(如遗传算法),用于优化晶圆厂内数千个工序的排程,以最大化产出 (Throughput)。

(4)硬件配置推荐:

-专用制造设备:

这是主要的“硬件”。价值数千万至数亿美元的专业设备,如 ASML 的 EUV 光刻机、Lam Research 的刻蚀机等。它们内部运行着高度定制的嵌入式控制系统。

- MES/YMS服务器:

CPU:Intel Xeon Scalable 或 AMD EPYC 服务器CPU,用于运行计算光刻、良率分析等大规模并行计算任务。

内存:TB级别的内存,用于处理全晶圆的量测数据和仿真。

存储:高性能、高可靠性的SAN/NAS存储阵列,容量可达PB级别,用于存储海量的工艺数据和配方。

网络:低延迟、高带宽的InfiniBand或高速以太网,确保设备与数据中心之间的实时通信。

3. 封装与测试

制造完成后,晶圆被送往封测厂 (OSAT),在这里芯片被切割、组装并进行最终测试。

(1)主要功能:

- 晶圆测试 (Wafer Probing): 在晶圆被切割前,使用探针卡测试每个裸片 (Die) 的基本功能,标记不合格的芯片。

- 封装 (Assembly):

- 切割 (Dicing): 将晶圆切割成单个的裸片。

- 贴片 (Die Attach): 将合格的裸片固定到基板或引线框架上。

- 引线键合 (Wire Bonding): 用极细的金属线(金或铜)将裸片上的焊盘连接到封装的引脚上。

- 最终测试 (Final Test): 将封装好的芯片放入自动测试设备 (ATE) 中,进行全面的功能、性能和压力测试,确保其在各种条件下(如不同温度)都能正常工作。

(2)主要软件工具:

- ATE 软件套件:

- Teradyne (泰瑞达):其 ATE(如 UltraFLEX 系列)运行基于Windows 的软件环境,使用 C++/Visual Studio 编写测试程序 (Test Program)。

- Advantest (爱德万):另一大 ATE 巨头,同样提供其专有的软件平台来开发测试程序。

- 测试程序 (Test Program Set, TPS):由测试工程师编写的特定软件,用于控制 ATE 硬件,向芯片发送测试向量 (Pattern),并接收和判断返回结果。

- 数据分析软件:用于分析 ATE 产生的海量测试数据 (通常为 STDF 格式),进行统计分析和良率诊断。

(3)主要算法:

- 测试向量生成 (ATPG):在设计阶段就使用算法自动生成一组最小的输入信号(向量),以最大化地覆盖芯片内部的潜在故障(如卡死故障、转移故障)。

- 内置自测试 (BIST):在芯片设计时就植入的逻辑,使芯片能够“自我测试”,ATE 只需启动测试并读取结果,这对于内存等规整电路非常高效。

- 信号处理算法:用于测试高速接口 (如 PCIe, DDR) 或模拟信号 (如 ADC/DAC),需要实时处理和分析复杂的波形。

(4)硬件配置推荐:

- ATE (自动测试设备):这是此阶段的核心硬件。它是来自Teradyne、Advantest、Cohu等公司的价值数百万美元的专用机台。它内部包含了高精度的电源、信号发生器、示波器和高速数字 I/O 通道。

- ATE 控制计算机:

- ATE 通常由一台多核心的 Windows PC 控制。

- 这台PC负责运行ATE的主软件、加载测试程序、与测试机台高速通信以及记录测试数据。硬件配置通常由ATE厂商指定,以确保兼容性和实时性能。

总结

半导体产业是一个紧密相连的链条:

- 设计 在高性能Linux工作站/服务器上运行EDA软件(Synopsys, Cadence, Siemens)。

- 制造 在晶圆厂中使用专用设备(ASML,Lam)和管理软件(MES,YMS)来执行生产。

- 封测 使用ATE设备(Teradyne, Advantest)和在其Windows 控制器上运行的C++ 测试程序来验证芯片质量。

史上最强大的--EDA/IC芯片/集成电路设计计算服务器存储集群配置方案

https://www.xasun.com/article/112/2799.html

我们专注于行业计算应用,并拥有10年以上丰富经验,

通过分析软件计算特点,给出专业匹配的工作站硬件配置方案,

系统优化+低延迟响应+加速技术(超频技术、虚拟并行计算、超频集群技术、闪存阵列等),

多用户云计算(内网穿透)

保证最短时间完成计算,机器使用率最大化,事半功倍。

上述所有配置,代表最新硬件架构,同时保证是最完美,最快,如有不符,可直接退货

欲咨询机器处理速度如何、技术咨询、索取详细技术方案,提供远程测试,请联系

UltraLAB图形工作站供货商:

西安坤隆计算机科技有限公司

国内知名高端定制图形工作站厂家

业务电话:400-705-6800

咨询微信号:100369800