硅基智能体的算力底座:ChipStack AI Super Agent 驱动的前端芯片设计硬件架构革命

时间:2026-03-02 21:45:18

来源:UltraLAB图形工作站方案网站

人气:71

作者:管理员

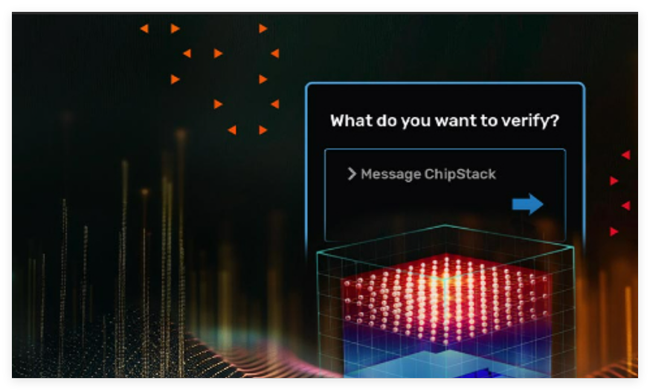

当 LLM Agent 遇见 RTL 代码生成,当形式验证遇上神经网络加速——重新定义数字 IC 设计的 EDA 工作站标准

在台积电 3nm 工艺节点的设计规则手册(DRM)已经膨胀到 2000+ 页的 2026 年,传统的前端芯片设计流程正面临算力瓶颈的临界点。一位资深数字 IC 设计师每天需要在 Cadence Genus 的综合报告、Synopsys VCS 的仿真波形、以及数千行 Verilog 代码之间进行上下文切换,而一次完整的回归验证(Regression)可能需要消耗数千核时的计算资源。

ChipStack™ AI Super Agent 的诞生,标志着芯片设计从"工具辅助"向"智能体驱动"的范式转移。这个集成了大语言模型(LLM)、强化学习(RL)优化器、以及多模态理解能力的 AI Agent,不仅能够自动生成符合 Timing/Area/Power 约束的 RTL 代码,更能通过智能验证策略将bug发现率提升 10 倍。然而,要驾驭这个"硅基大脑",传统的办公电脑已力不从心——你需要一套专为 AI-Native EDA 设计的算力架构。

第一章:ChipStack™ AI Super Agent 的技术画像——为什么需要专用硬件?

ChipStack™ 代表了 EDA 工具的第三代进化:

第一代(传统 EDA):人工编写 RTL → 综合 → 仿真 → 反复迭代,依赖工程师经验 第二代(辅助 EDA):AI 辅助代码补全(GitHub Copilot for Verilog)、智能 linter,但仍是被动工具 第三代(Agentic EDA):ChipStack™ AI Super Agent 作为主动智能体,具备:

-

自主规划(Planning):将高层 spec(如"设计一个支持 RV64GC 的乱序执行 CPU")分解为模块级任务

-

代码生成(Coding):基于内部训练的数字电路大模型(可能达 70B+ 参数)生成 SystemVerilog

-

验证代理(Verification):自动生成 UVM testbench,利用强化学习探索边界条件

-

优化循环(Optimization):与逻辑综合工具交互,通过 DSE(设计空间探索)自动调整架构参数

硬件需求的质变:

传统前端设计主要依赖 CPU(高主频、大缓存),而 ChipStack™ 引入了三个新的算力维度:

-

大模型推理负载:每次代码生成需要加载 70B 参数(FP16 约需 140GB 显存或 INT4 量化后 35GB+)

-

并行验证加速:需要 GPU 加速 RTL 仿真(如 Synopsys VCS 的 GPU 加速模式)或形式验证的 SAT 求解

-

多智能体协作:多个 Agent 实例同时运行(架构 Agent、验证 Agent、综合 Agent),需要高内存容量支撑多进程

第二章:核心算力架构——"脑-眼-手"分离设计

针对 ChipStack™ 的 Agentic Workflow,我们提出三层异构硬件架构:

认知层(Cognition Layer):AI Agent 的"大脑"

负责运行 ChipStack™ 的核心 LLM(可能是基于 Llama 3 或 Qwen 2.5 微调的电路专用模型)。

关键指标:

-

显存容量:决定能运行的模型规模。对于 70B 参数的电路代码生成模型,建议 48GB+ 显存(RTX 6000 Ada 或 A100 80GB)

-

推理吞吐量:代码生成是 token-by-token 的流式输出,需要 >50 tokens/s 才能保持流畅的"结对编程"体验

-

多实例隔离:支持同时运行 3-5 个 Agent 实例(架构探索、代码生成、验证并行),显存需求线性增长

推荐配置:

-

GPU:NVIDIA RTX 6000 Ada Generation 48GB × 2(NVLink 桥接,显存池化至 96GB)

-

优势:96GB 显存可完整加载 70B FP16 模型 + KV Cache,或同时运行两个 34B Agent 实例(架构 Agent + 验证 Agent)

-

ECC 纠错:7×24 小时设计自动化过程中防止显存错误导致 Agent 崩溃

-

CUDA 核心:18176 个核心加速 Transformer 解码

-

执行层(Execution Layer):传统 EDA 的"肌肉"

负责运行实际的逻辑综合、仿真、形式验证工具(Cadence/Synopsys/Mentor)。

关键指标:

-

单核性能:EDA 工具(特别是综合和布局布线)有大量单线程操作,需要 高主频(>5.0GHz) 和 大 L3 缓存(>64MB)

-

内存带宽:逻辑综合过程中频繁访问设计数据库(MMMC 分析需要同时加载多个 corner 的库文件),建议 8 通道 DDR5-5600(带宽 >400GB/s)

-

内存容量:大型 SoC 设计(如手机芯片 AP)综合时需要 512GB-1TB 内存 存储网表和约束

推荐配置:

-

CPU:AMD Ryzen Threadripper PRO 7995WX(96 核 192 线程,5.15GHz 睿频,384MB L3 缓存)

-

优势:96 核可并行运行多个综合任务(Exploration mode),大缓存加速设计数据库查询

-

-

内存:512GB DDR5-5600 ECC REG(8 通道,16×32GB)

-

扩展性:主板支持 2TB 总容量,满足未来 3nm/2nm 更大规模设计需求

-

-

存储:8TB NVMe Gen5 SSD(读取 14GB/s,存储数百万个设计文件)

交互层(Interaction Layer):工程师的"窗口"

负责多模态交互界面——代码编辑器、波形查看器、AI Agent 对话界面、以及实时的功耗/时序可视化。

关键指标:

-

显示输出:需要同时显示 4-6 个 4K 显示器(左:RTL 代码;中:AI Agent 对话;右:综合报告;上:波形;下:架构图)

-

色彩精度:电路设计的 schematic 和版图需要 10-bit 色深,确保电压/温度热力图的色彩层次准确

-

低延迟:AI Agent 的流式回复需要 <50ms 的显示延迟

推荐配置:

-

GPU:与认知层共用 RTX 6000 Ada(支持 4×DisplayPort 2.0,单卡可驱动 4 台 4K@120Hz 显示器)

-

显示器:27 英寸 4K IPS × 4(Dell U2723QE 或同等级,支持 USB-C 一线通)

-

输入设备:支持宏编程的机械键盘(快速触发 Agent 指令)+ 高精度鼠标(波形缩放)

第三章:场景化配置方案——从个人极客到企业级设计中心

方案 A:个人开发者/Super Solo(ChipStack™ Lite)

预算:8-12 万元 目标:单人完成百万门级 ASIC 的前端设计,AI Agent 辅助编码与验证

硬件清单:

-

GPU:NVIDIA RTX 4090 24GB(水冷改装版,INT4 量化可运行 70B 模型,或原生运行 34B 模型)

-

CPU:Intel Core i9-14900K(6.0GHz 睿频,加速综合工具单线程操作)

-

内存:128GB DDR5-6000(双通道,支持中等规模设计)

-

存储:2TB NVMe Gen4(系统)+ 4TB NVMe(设计库)

-

显示:双 27 英寸 4K 显示器(代码 + Agent 界面)

-

网络:2.5GbE(连接公司内部设计服务器)

软件栈:

-

ChipStack™ AI Agent(本地部署 34B 模型)

-

Vivado / Quartus(FPGA 原型验证)

-

Verilator(开源仿真,轻量级)

性能预期:

-

自动生成 10,000 行 Verilog 代码:约 2-3 分钟(流式生成)

-

单元模块综合:10 万门规模,5 分钟内完成

-

本地仿真:每秒 1000+ cycles(中等复杂度)

方案 B:设计团队/ChipStack™ Studio(3-5 人团队)

预算:35-45 万元/套,共 3-5 套 目标:复杂 SoC 前端设计(千万门级),多 Agent 协作(架构师 Agent + 验证 Agent + 综合 Agent)

硬件清单:

-

GPU:RTX 6000 Ada 48GB × 2(NVLink,共 96GB,支持多 Agent 实例)

-

CPU:AMD Threadripper PRO 5995WX(64 核 128 线程,5.0GHz)

-

内存:256GB DDR5-4800 ECC(支持多项目并行)

-

存储:8TB NVMe SSD(RAID 0)+ 16TB HDD(备份)

-

网络:10GbE(连接 LSF/SGE 作业调度集群)

-

显示:三屏 27 英寸 4K(多 Agent 窗口并行监控)

特色配置:

-

硬件安全模块(HSM):用于保护 ChipStack™ 的模型权重和生成的 IP 核(防止泄露)

-

高速缓存层:Intel Optane P5800X(持久内存,加速设计数据库随机读写)

软件栈:

-

ChipStack™ Enterprise(支持多 Agent 协作)

-

Cadence Genus / Innovus(综合与布局)

-

Synopsys VCS(仿真,支持 GPU 加速)

-

Perforce Helix Core(版本控制,大文件支持)

方案 C:企业级设计中心/ChipStack™ Hub(50+ 工程师)

预算:单节点 80-120 万元,共 10-20 节点 目标:先进工艺(3nm/2nm)芯片设计,AI Agent 7×24 小时自动优化,与现有 EDA 云流程集成

硬件架构: AI Agent 推理集群(专用):

-

GPU:NVIDIA H100 80GB × 8(DGX H100 或等效)

-

功能:运行 ChipStack™ 的 405B 参数超级模型(或 MoE 架构模型),支持全公司工程师并发调用

-

网络:InfiniBand NDR 400Gb/s(低延迟 API 响应)

EDA 计算节点(通用):

-

CPU:双路 AMD EPYC 9655(96 核/路,共 192 核)

-

内存:1TB DDR5-5600(支持亿门级设计综合)

-

加速卡:Synopsys ZeBu / Cadence Palladium(硬件仿真加速器,与 ChipStack™ Agent 集成)

交互终端(每人):

-

瘦客户端:UltraLAB 图形工作站(RTX A4000 16GB,驱动 4 屏),通过 Teradici/HP Anyware 连接到中央设计库

存储架构:

-

热数据:100TB NVMe 全闪存阵列(Lustre 并行文件系统,存储活跃设计)

-

温数据:500TB SAS SSD(历史版本、验证波形)

-

冷数据:PB 级磁带库(归档)

第四章:ChipStack™ 专属优化——软件与硬件的协同

为了最大化 ChipStack™ AI Super Agent 的性能,硬件配置需要配合特定的软件优化:

1. 模型量化与硬件匹配

-

FP16(16-bit):需要 48GB+ 显存(RTX 6000 Ada 单卡),精度最高,适合最终签核(Sign-off)阶段的精确优化

-

INT8/FP8(8-bit):需要 Ada/Hopper 架构(RTX 4090/5090、A100/H100),速度提升 2 倍,适合日常迭代

-

INT4(4-bit):可在 24GB 显存运行 70B 模型,适合个人开发者,但复杂逻辑推理能力略有下降

2. 内存分层策略(Memory Tiering) ChipStack™ 会产生海量中间数据(生成的代码变体、验证报告、综合日志),建议:

-

L1(显存):存放当前活跃的 LLM 参数和 KV Cache

-

L2(DRAM):存放设计数据库和待处理的代码文件(512GB-1TB)

-

L3(NVMe SSD):存放历史设计版本和波形文件(10TB+)

-

L4(网络存储):归档数据

3. 网络拓扑(多 Agent 协作) 当多个 ChipStack™ Agent 实例协同工作时(如一个 Agent 生成代码,另一个 Agent 实时审查):

-

使用 RDMA over Converged Ethernet (RoCE v2) 降低 Agent 间通信延迟

-

配置 PCIe 5.0 Switch 实现 GPU 与 GPU 之间的 P2P Direct 通信(避免经过 CPU 内存)

4. 散热与可靠性 ChipStack™ 设计任务常需连续运行数天(如自动 DSE 探索):

-

水冷系统:定制分体式水冷(CPU + 双 GPU),满载噪音 <40dB(办公室环境友好)

-

冗余电源:1+1 冗余钛金电源(确保长时间运行不中断)

-

UPS:在线式 UPS(防止断电导致 Agent 状态丢失和设计数据损坏)

第五章:投资回报分析(ROI)——为什么要买这些硬件?

传统前端设计流程 vs ChipStack™ AI Super Agent:

| 指标 | 传统流程(人工) | ChipStack™ + 推荐硬件 | 提升倍数 |

|---|---|---|---|

| 代码生成速度 | 100 行/小时(人工编写) | 1000 行/小时(AI 生成 + 人工审查) | 10× |

| Bug 发现时间 | 平均 3 天(仿真暴露) | 平均 2 小时(AI 形式验证) | 36× |

| 综合迭代次数 | 50 次(人工调整约束) | 200 次(AI 自动 DSE) | 4× |

| TTM(上市时间) | 12 个月 | 6 个月 | 2× |

成本对比:

-

硬件投入:方案 B(40 万元)相当于一位资深数字 IC 设计师 6 个月的薪资

-

节省成本:缩短 6 个月 TTM,对于千万美元级芯片项目,意味着节省 500 万美元+ 的机会成本

-

人力优化:初级工程师 + ChipStack™ 可达到资深工程师的产出,降低人力成本 40%

结语:硅基智能体的时代已来

ChipStack™ AI Super Agent 不是简单的"EDA 插件",而是芯片设计领域的"副驾驶"——它理解你的架构意图,自动生成实现,智能验证功能,并持续优化性能。但要释放这个超级智能体的全部潜力,你需要为之配备超级算力底座。

从 RTX 4090 的个人工坊,到 H100 集群的企业大脑,UltraLAB 为 ChipStack™ 生态提供全谱系的硬件支持。 让我们用足够的显存承载模型的智慧,用足够的内存容纳设计的复杂度,用足够的算力压缩创新的周期。

在 AI 定义芯片设计的时代,算力即创造力。

【UltraLAB 技术团队 | AI-Native EDA 算力架构专家】

咨询专线:400-4076-800

微信号:xasun001