硅基智慧的觉醒:生成式AI重构芯片设计范式——Synopsys.ai Copilot 全栈硬件架构深度解析

时间:2026-03-03 15:30:39

来源:UltraLAB图形工作站方案网站

人气:184

作者:管理员

当大语言模型遇见3nm晶体管,当自然语言对话驱动RTL生成——支撑"AI设计芯片"的算力底座该如何构建?

在台积电3nm工艺节点单芯片集成超过1000亿晶体管的今天,一位资深数字IC设计师正面临前所未有的认知过载:他需要同时理解RISC-V指令集扩展、低功耗设计策略(UPF/CPF)、先进封装(Chiplet)的互连约束,以及千行SystemVerilog代码中的微妙时序违例。传统的设计流程如同在迷宫中原子化探索——每一个架构决策、每一次综合迭代、每一轮验证回归,都消耗着数周的人力与算力。

直到生成式AI的介入。Synopsys.ai Copilot的登场,标志着EDA工具从"自动化"向"自主化"的质变:设计师用自然语言描述"需要一个支持AI加速的NPU,功耗预算5W,面积小于10mm²",AI在几分钟内生成可选的架构方案、对应的RTL代码框架、以及初步的PPA(功耗-性能-面积)分析报告。这不仅是效率的提升,更是芯片设计民主化的开端——让架构师专注于创新,让AI承担繁琐的实现细节。

然而,这场变革的幕后英雄,是支撑海量参数模型(LLM)推理与EDA工具链协同的专用硬件架构。当Copilot需要同时解析百万行代码库、实时生成验证激励、并在多目标空间中寻找帕累托最优解时,普通的办公工作站会在第一时间崩溃。

第一章:生成式AI解锁的芯片设计新维度

生成式AI正在重塑芯片设计的全生命周期,其影响远超简单的"代码补全":

1.1 自然语言驱动的RTL架构生成(DSO.ai进化版)

传统RTL编写需要设计师精通Verilog/SystemVerilog语法与硬件描述范式。生成式AI通过理解自然语言规格书(如"实现一个支持乱序执行的四发射RISC-V核心,分支预测准确率>95%"),可自动生成:

-

可综合的RTL代码(符合语法与综合约束)

-

微架构文档(自动生成的Markdown/Word设计说明)

-

测试策略建议(基于代码覆盖率的验证计划)

技术挑战:需要大语言模型(如GPT-4级别)理解硬件描述语言的严格语义,避免生成"仿真可过但综合失败"的代码。

1.2 验证空间的智能爆炸(VSO.ai增强)

芯片验证通常占据项目周期的70%。生成式AI可以:

-

自动生成UVM testbench:从设计规格提取测试点,生成随机约束(SystemVerilog constraint)

-

智能调试:分析失败日志,定位根本原因(如"第47行的时序违例源于时钟域 crossing 缺少同步器")

-

覆盖闭合助手:识别未覆盖的代码路径,建议针对性的定向测试

技术挑战:需要处理TB级仿真波形数据,结合时序分析工具(如Verdi)进行多模态理解。

1.3 多目标设计空间探索(DSE)的AI代理

在3nm工艺下,PPA优化是一个高维非凸问题。生成式AI作为智能代理,能够:

-

自动探索综合策略:尝试不同的编译指令(compile_ultra vs compile),预测QoR(Quality of Results)

-

布局布线助手:在Innovus/ICC2中,通过强化学习优化floorplan,减少 congestion

-

知识重用:从企业历史设计库(IP库)中学习,推荐复用现有模块或生成衍生设计

1.4 模拟与混合信号的AI革命(ASO.ai)

模拟电路设计长期依赖专家经验。生成式AI可以:

-

电路拓扑生成:根据 specs(增益>60dB,带宽>1GHz)生成Op-Amp电路图

-

参数优化:自动调整晶体管尺寸(W/L),使用贝叶斯优化+神经网络代理模型

-

迁移学习:将成熟工艺节点(28nm)的设计知识迁移到先进节点(3nm)

第二章:Synopsys.ai Copilot 技术架构揭秘

Synopsys.ai Copilot并非单一工具,而是一个云-边协同的AI-EDA生态系统:

2.1 核心架构:Azure OpenAI + 领域专用模型

-

基础模型:基于Microsoft Azure OpenAI Service(GPT-4级别大模型),提供自然语言理解与代码生成能力

-

领域适应:Synopsys在数十亿行开源/授权RTL代码、数百万小时仿真数据上微调,形成芯片设计专用LLM

-

RAG(检索增强生成):连接企业私有设计知识库(IP规格、约束文件、历史bug报告),确保生成内容的领域相关性

2.2 功能模块与硬件映射

表格

| 模块 | AI能力 | 计算需求 | 硬件加速点 |

|---|---|---|---|

| DSO.ai Copilot | RTL生成/优化 | 大模型推理(70B+参数) | GPU(TensorRT-LLM优化) |

| VSO.ai Copilot | 验证智能体 | 波形数据分析+LLM | GPU+大内存(波形缓存) |

| ASO.ai Copilot | 模拟设计 | 电路仿真+贝叶斯优化 | CPU并行(SPICE加速) |

| Knowledge Bot | 企业知识问答 | 向量数据库检索 | NVMe SSD(低延迟检索) |

2.3 部署模式:云端 vs 本地

-

云端模式(Synopsys-hosted):模型运行在Synopsys云,用户通过API调用,适合中小型企业,数据需脱敏

-

混合模式:LLM推理在本地(私有部署),EDA工具在云端,平衡数据安全与算力弹性

-

本地私有部署(On-premise):完整AI-EDA环境部署在企业数据中心,适合军工/高端芯片(涉密要求)

第三章:硬件配置的技术瓶颈与突破

支撑Synopsys.ai Copilot的硬件面临三重挑战:LLM推理的显存墙、EDA数据的I/O墙、多任务并行的调度墙。

3.1 LLM推理的显存与带宽瓶颈

Copilot的核心是一个经过微调的大语言模型(预估70B-130B参数范围):

-

显存需求:FP16精度下,130B模型需260GB显存;INT8量化后仍需130GB

-

推理延迟:生成1000行RTL代码(约3000 tokens)需在10秒内完成,要求>50 tokens/s的吞吐量

-

内存带宽:Transformer解码是内存带宽密集型,需>1TB/s的显存带宽(HBM2e/3)

解决方案:

-

多卡并行:2×NVIDIA H100 80GB(NVLink)或 4×A100 80GB

-

量化推理:使用FP8/INT8精度(Synopsys可能采用NVIDIA Transformer Engine)

-

分页注意力:vLLM等框架减少KV Cache碎片,提升显存利用率

3.2 EDA数据湖的存储架构

Copilot需要实时访问:

-

设计数据库:百万行RTL、SDC约束、UPF电源意图文件(PB级历史数据)

-

仿真波形:VCD/FSDB文件(单次仿真可达TB级)

-

知识图谱:企业IP库、工艺库(PDK)、设计规则(DRC/LVS)

存储需求:

-

热数据层:全闪存NVMe阵列(>10GB/s带宽,加载大型设计<30秒)

-

温数据层:对象存储(MinIO/Ceph),存储历史版本与仿真结果

-

向量数据库:Milvus/Pinecone,存储设计Embedding(用于RAG检索)

3.3 异构计算的调度复杂性

Copilot运行时涉及:

-

CPU:解析设计数据库、运行轻量级仿真(RTL仿真)

-

GPU:LLM推理、波形数据分析(CNN识别信号模式)

-

FPGA:可选的硬件仿真加速(Palladium/Zebu)

需要统一调度:Kubernetes+Slurm混合调度,确保GPU资源不被传统EDA任务占用。

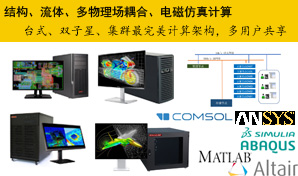

第四章:UltraLAB AI-EDA工作站与集群配置

针对Synopsys.ai Copilot的硬件需求,UltraLAB提供三级配置方案:

配置A:AI辅助设计工作站(个人/小团队)

定位:架构师/高级工程师,本地部署轻量化Copilot(7B-13B参数模型),连接云端完整版

硬件规格:

-

CPU:AMD Ryzen Threadripper PRO 5995WX(64核,高主频加速RTL编译)

-

GPU:NVIDIA RTX 6000 Ada 48GB(大显存支持13B模型INT8推理,ECC纠错确保长时间运行稳定)

-

内存:256GB DDR5-4800 ECC(缓存大型设计文件,支持本地向量数据库)

-

存储:

-

系统盘:2TB NVMe Gen5(Synopsys工具链+本地LLM权重)

-

数据盘:8TB NVMe SSD(当前项目设计库)

-

归档:20TB HDD(历史项目)

-

-

网络:10GbE(连接企业中心服务器)

-

显示:双27英寸4K(左:RTL编辑器;右:Copilot对话界面+波形查看器)

软件栈:

-

Windows 11 Pro for Workstations + WSL2(Ubuntu 22.04)

-

Synopsys Design Compiler + VCS + Verdi(本地EDA工具)

-

Ollama(本地部署CodeLlama-13B,脱敏辅助编码)

-

云端API:Synopsys.ai Copilot(通过VPN/专线连接)

预估价格:18-22万元

配置B:企业级AI-EDA私有云(10-50人团队)

定位:完整本地部署Copilot,数据不出域,支持多用户并发

硬件架构:

AI推理节点(2台):

-

GPU:4×NVIDIA H100 80GB(NVLink,总显存320GB,支持130B模型FP16推理)

-

CPU:双路AMD EPYC 9655(96核/路,处理多并发请求)

-

内存:1TB DDR5-5600(存储RAG向量索引)

-

功能:运行Synopsys.ai Copilot本地实例,支持20设计师同时对话

EDA计算节点(4台):

-

CPU:双路EPYC 9554(64核/路)

-

内存:512GB/节点(运行VCS并行仿真)

-

GPU:RTX A4000(轻量级任务,如Verdi可视化)

存储系统:

-

全闪存阵列:100TB NVMe SSD(RAID 10),存储活跃项目(100+设计版本)

-

对象存储:500TB HDD集群,归档历史数据

-

向量数据库服务器:专用节点(128GB内存,Milvus集群),存储设计知识Embedding

网络:

-

100GbE InfiniBand(AI节点与EDA节点间高速互连)

-

25GbE以太网(用户接入)

预估价格:300-400万元(含Synopsys许可证)

配置C:超大规模AI设计中心(大型芯片企业/云服务商)

定位:支撑千卡级芯片设计,自研大模型微调,多项目并行

硬件架构:

-

AI训练集群:8×NVIDIA DGX H100(用于微调企业专用芯片设计LLM)

-

推理集群:32×H100(支撑500+设计师同时使用Copilot)

-

EDA超级计算:1024×CPU核心(Synopsys Fusion Compiler并行)

-

存储:5PB全闪存(Pure Storage//N系列)+ 20PB HDD(冷数据)

-

网络:NVIDIA Quantum-2 InfiniBand(400Gb/s,全互联拓扑)

特色功能:

-

数字孪生设计:AI实时预测PPA,数字孪生体与实际芯片同步进化

-

自动设计代理:AI Agent自主运行设计迭代( overnight optimization)

预估价格:5000万+(超算中心级)

第五章:投资回报与未来演进

5.1 效率提升量化(基于Synopsys公开数据)

-

RTL生产力:首版RTL生成时间缩短10倍(从数周到数天)

-

验证效率:测试覆盖率提升20%,调试时间减少50%

-

PPA优化:AI驱动的DSE探索10,000+架构方案,人类设计师仅能探索<100个,最终PPA提升15-30%

-

知识重用:新员工通过Copilot查询企业知识库,上手时间从6个月缩短至1个月

5.2 硬件投资回报(ROI)计算

以配置B(400万元)为例:

-

节省人力:10名设计师×50%效率提升×年薪50万 = 年节省250万

-

缩短TTM:芯片提前3个月上市,假设市场窗口价值1000万/月 = 3000万收益

-

硬件折旧:3年折旧,年均成本133万

-

净ROI:(250万+1000万)/133万 ≈ 940%(考虑TTM收益)

5.3 技术演进路线(2025-2030)

-

2025:Copilot辅助编码(当前阶段)

-

2026:AI自主完成模块级设计(从spec到GDSII的自动化)

-

2028:AI设计芯片(人类仅需定义高层架构,AI完成微架构到物理实现)

-

2030:AI驱动的"硅基进化"——芯片自我优化架构(Self-Evolving Chips)

结语:人机协同的硅基未来

Synopsys.ai Copilot不是替代设计师,而是将人类从繁琐的语法细节中解放,专注于架构创新与系统优化。就像CAD软件没有取代建筑师,而是让建筑更宏伟一样,AI-EDA工具将推动芯片设计进入"百倍生产力"时代。

UltraLAB AI-EDA算力解决方案,以覆盖从个人工作站到企业私有云的硬件架构,为这场硅基革命提供坚实的算力底座。从大模型推理到波形分析,从RTL生成到物理验证,我们确保每一次AI对话、每一次设计迭代、每一次创新突破,都有可靠的硬件支撑。

让AI设计芯片,让硬件支撑AI——这就是半导体行业的未来。

【UltraLAB EDA解决方案事业部 | AI芯片设计算力架构专家】

咨询专线:400-7056-800

微信号:xasun001