雷达干扰决策模型算法研究:实时信号处理对工作站硬件的严苛要求

时间:2026-02-25 21:54:31

来源:UltraLAB图形工作站方案网站

人气:81

作者:管理员

——从微秒级脉内分析到毫秒级干扰注入,电子战智能决策系统的算力底座该如何构建?

引言:当电子战进入"智能认知"时代,算力即战斗力

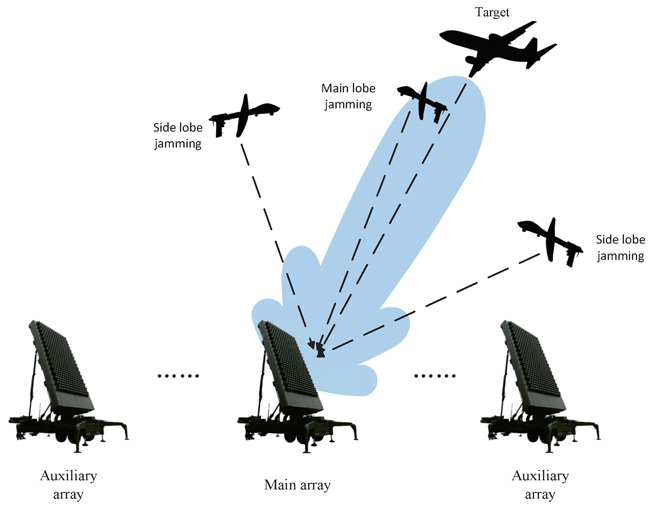

在现代电磁频谱战场上,雷达与干扰机的博弈已从传统的"噪声压制"演进为"认知对抗"。新一代有源相控阵雷达(AESA)采用捷变频、脉内调制、波形捷变等低截获概率(LPI)技术,其信号特征在微秒级时间尺度上动态变化。传统的基于规则库的干扰决策系统已难以应对这种"雷达-干扰"快速博弈,基于深度学习威胁识别与强化学习干扰策略优化的智能决策模型正在成为研究热点。

然而,这类算法的工程化部署面临一个严峻的物理约束:从雷达信号截获到干扰样式生成的全流程延迟必须控制在毫秒级(甚至亚毫秒级)。这意味着,在实验室环境中验证有效的干扰决策算法,当面对500MHz以上瞬时带宽、GHz级采样率的宽带数字接收机数据流时,往往遭遇"算法有效但硬件来不及"的窘境——CPU满载导致的决策延迟、GPU显存交换引发的卡顿、PCIe总线拥塞造成的丢帧,都可能让精心设计的干扰策略在实战中错失最佳注入时机。

作为深耕高性能计算与实时信号处理硬件领域的UltraLAB,我们在服务国防科技大学、中电科某研究所、航天科工集团等单位的雷达对抗预研项目中,深刻洞察到:雷达干扰决策模型的硬件平台绝非普通的"高配PC",而是需要满足确定性低延迟、高吞吐持续计算、多异构处理器协同的专用实时计算架构。本文将从算法特征出发,深度解析实时信号处理对工作站硬件的严苛要求,并给出针对性的UltraLAB异构加速方案。

一、雷达干扰决策模型的计算特征与实时性瓶颈

1.1 算法流程的"时间切片"分析

一个典型的认知雷达干扰决策系统包含以下计算阶段,每个阶段都有严苛的延迟预算:

阶段一:前端信号处理(微秒级)

-

数字下变频(DDC):将GHz级中频信号降采样至基带,涉及CIC滤波、FIR滤波

-

短时傅里叶变换(STFT):10μs滑窗内的频谱分析,用于脉冲检测(PDW生成)

-

脉内特征提取:瞬时频率测量(IFM)、Chirp速率估计、BPSK/QPSK调制识别

-

硬件需求:FPGA或GPU的确定性延迟,要求处理延迟 < 信号驻留时间的10%

阶段二:威胁识别与态势评估(毫秒级)

-

脉冲描述字(PDW)流聚类:DBSCAN/Mean-Shift算法对高密度脉冲流(>100万脉冲/秒)进行分选

-

辐射源个体识别(SEI):基于CNN或Transformer的"雷达指纹"识别,需推理ResNet-50级网络

-

威胁等级评估:基于模糊逻辑或贝叶斯网络的威胁排序

-

硬件需求:GPU并行推理,要求单次推理延迟 < 5ms,批量处理支持高并发PDW流

阶段三:干扰策略决策(毫秒级)

-

强化学习策略网络:基于当前态势(State)输出最优干扰动作(Action),如转发延迟、噪声调制样式

-

博弈论优化:纳什均衡求解或Stackelberg博弈模型,涉及矩阵运算与迭代优化

-

硬件需求:低精度FP16/INT8推理优化,支持模型并行与流水线并行

阶段四:干扰波形合成与发射(微秒级)

-

DRFM(数字射频存储)控制:精确控制干扰信号的延迟、多普勒频移、相位调制

-

闭环校准:根据反馈信号实时调整干扰功率(基于梯度下降的自适应算法)

-

硬件需求:硬实时(Hard Real-time)响应,抖动(Jitter)< 1μs

1.2 数据流的"带宽墙"与"延迟墙"

带宽墙(Memory Wall):

-

宽带接收机(2GHz带宽,14bit ADC)的原始数据率:>7GB/s(双通道I/Q数据)

-

高分辨率频谱分析(32768点FFT,50%重叠率)的运算强度:>500 GFLOPS/s

-

多通道并行处理(4通道干涉仪测向):数据率与算力需求线性倍增

延迟墙(Latency Wall):

-

操作系统调度抖动:Windows/Linux标准内核的调度延迟可达10-100ms,无法满足硬实时要求

-

PCIe传输延迟:CPU与GPU间通过PCIe 4.0 x16传输1GB数据,理论延迟约12ms(含协议开销)

-

存储I/O延迟:标准NVMe SSD的4K随机读写延迟约10μs,但对于连续大流量写入,队列深度饱和后延迟剧增

二、硬件瓶颈深度解构:为什么普通服务器无法胜任?

瓶颈一:CPU的"阿姆达尔困境"

现代雷达信号处理算法虽可并行化,但存在强串行依赖:

-

脉冲检测后的TOA(到达时间)解算必须按时间顺序

-

自适应滤波器的系数更新存在数据依赖

-

博弈论决策中的迭代求解需等待收敛

普通服务器的缺陷:

-

至强可扩展处理器(Xeon Scalable)虽核数多(64核+),但基频低(2.0GHz),单核性能不足,导致串行环节成为瓶颈

-

超线程技术(Hyper-Threading)在实时信号处理中引入不确定性,两个逻辑核争抢物理核资源导致延迟抖动

UltraLAB解决方案:

采用Intel Xeon W-3400系列或AMD Ryzen Threadripper PRO 7000 WX系列:

-

高基频(>3.5GHz)保证单核串行性能

-

关闭超线程,启用"核隔离"(Core Isolation),将特定物理核绑定给实时任务(Real-time Priority)

-

使用PREEMPT_RT实时Linux补丁,将内核调度延迟降至<50μs

瓶颈二:GPU的"显存墙"与"同步开销"

深度学习推理虽然适合GPU加速,但存在隐性成本:

-

模型加载延迟:从主机内存(DRAM)拷贝模型权重至GPU显存(HBM),大模型(如Transformer)可能需要数百毫秒

-

PCIe传输瓶颈:原始IQ数据从采集卡经CPU内存中转至GPU,PCIe 4.0 x16的理论带宽32GB/s,实际有效带宽约25GB/s,对于7GB/s的数据流,仅剩3倍余量,一旦数据突发(Burst Traffic)即导致丢帧

-

内核启动延迟:CUDA Kernel启动开销约5-10μs,对于微秒级的信号处理,累积延迟不可忽视

UltraLAB优化策略:

-

GPUDirect RDMA:支持采集卡(如Spectrum Instrumentation、Keysight UXR)直接通过PCIe P2P传输数据至GPU显存,零拷贝(Zero-Copy)架构消除CPU内存中转延迟

-

持久化CUDA Context:预加载模型至显存并保持常驻,避免运行时加载延迟

-

多流(Multi-Stream)并行:利用CUDA Stream实现计算与数据传输重叠(Overlap),隐藏延迟

瓶颈三:存储系统的"写入悬崖"

雷达对抗试验需长时间记录原始IQ数据用于事后分析(Post-analysis):

-

连续记录2小时,2GHz带宽数据总量:>50TB

-

标准SATA SSD(500MB/s)需要28小时才能写入,完全不可接受

-

消费级NVMe SSD(3GB/s)虽速度提升,但面临写入放大(Write Amplification)与过热降速(Thermal Throttling)问题,持续写入30分钟后速度可能暴跌至500MB/s

UltraLAB存储方案:

-

企业级U.2 NVMe RAID阵列:8×7.68TB Intel P5510企业级SSD组建RAID 0,持续写入速度>20GB/s,支持PLP(掉电保护),确保数据完整性

-

分层存储架构:热数据(最近1小时)存放于NVMe,温数据自动迁移至SAS HDD(RAID 6),冷数据归档至LTO-9磁带库

-

内存虚拟盘(RAM Disk):将128GB系统内存划分为虚拟磁盘,用于存储关键中间变量,实现纳秒级访问延迟

瓶颈四:多卡协同的"时钟同步"难题

复杂系统通常需要多通道采集卡与多GPU协同:

-

4通道相干采集卡(用于干涉仪测向)需严格同步采样时钟(<1ps抖动)

-

多GPU并行推理(模型并行或数据并行)需同步梯度或中间结果

普通工作站的缺陷:

-

多GPU通过PCIe Switch连接,通信需经过CPU根复合体(Root Complex),延迟高

-

缺乏硬件级时间同步(IEEE 1588 PTP或White Rabbit协议)

UltraLAB架构设计:

-

NVLink Bridge:对于NVIDIA A100/A6000,使用NVLink实现GPU间900GB/s的高速直连,适合模型并行

-

SyncE/PTP授时:集成高精度时钟板卡(如Spectracom TSync),实现系统级微秒级时间同步

-

PCIe Fabric架构:使用PCIe交换芯片(Broadcom PEX9797)构建无阻塞PCIe网络,支持多采集卡直连多GPU

三、UltraLAB雷达干扰决策工作站架构方案

针对上述瓶颈,UltraLAB提出"低延迟异构计算架构"(Low-Latency Heterogeneous Computing Architecture, LL-HCA):

配置方案A:实验室研发平台(算法验证与模型训练)

目标:支持PyTorch/TensorFlow模型开发,同时具备实时信号处理接入能力

硬件配置:

-

CPU:AMD Ryzen Threadripper PRO 7995WX(96核192线程,基频2.5GHz,睿频5.1GHz)

-

选型逻辑:八通道DDR5(峰值带宽>400GB/s),支持大量IQ数据预处理

-

-

GPU:2× NVIDIA RTX 6000 Ada Generation(48GB GDDR6 ECC,支持NVLink)

-

支持FP8/FP16混合精度推理,显存容量支持大模型(如LLM-based决策模型)驻留

-

-

FPGA加速:1× Xilinx Alveo U55C(用于HLS开发的前端信号处理算法验证)

-

内存:512GB DDR5-4800 ECC(16×32GB),支持大batch训练

-

存储:系统盘2TB NVMe Gen4 + 数据池8TB NVMe RAID 0(U.2企业级)

-

I/O:双端口100GbE(NVIDIA ConnectX-6),支持高速数据摄入

软件优化:

-

预装NVIDIA Holoscan SDK,支持从信号采集到AI推理的流水线开发

-

配置实时Linux内核(PREEMPT_RT),确保关键线程不被抢占

-

集成CUDA-X Signal Processing库(cuFFT、cuBLAS、cuSOLVER)

配置方案B:外场/内场实时处理平台(工程化部署)

目标:满足严苛的实时性(<10ms端到端延迟)与可靠性(7×24小时运行)

硬件配置:

-

CPU:Intel Xeon W9-3495X(56核,睿频4.8GHz,支持睿频加速Max 3.0)

-

启用Intel TCC(Time Coordinated Computing)特性,提供时间同步与确定性执行

-

-

GPU:4× NVIDIA RTX A4000(16GB,单槽设计,适合多卡密集部署)

-

采用模型并行策略,将不同雷达威胁识别任务分配至不同GPU,降低单卡负载

-

-

采集接口:集成PCIe Gen3 x8的高速ADC卡(如Keysight M9203A或Ettus USRP X440)

-

存储:RAID 0阵列(4×4TB NVMe),支持>10GB/s持续写入,配备独立散热风道

-

机箱:4U机架式工业机箱,前置热插拔硬盘位,冗余电源(CRPS),-20℃~60℃宽温运行能力

可靠性设计:

-

ECC显存与内存:自动纠正单比特错误,检测双比特错误,防止宇宙射线导致的决策误判

-

看门狗定时器(Watchdog Timer):软件卡死时自动复位,确保系统可用性>99.9%

-

光纤隔离:射频前端通过光纤与工作站连接,消除地环路干扰与EMC问题

配置方案C:分布式决策集群(多平台协同对抗)

目标:支持多干扰站协同、云端模型更新、大数据态势分析

架构组成:

-

边缘节点:多台配置B平台,部署于各干扰站,负责本地实时决策

-

中心服务器:UltraLAB双路服务器(2× Intel Xeon Gold 6458Q),负责全局态势融合与模型训练

-

高速互联:InfiniBand HDR(200Gbps)或100GbE RoCE v2,支持GPUDirect RDMA跨节点通信

-

时间同步:White Rabbit高精度以太网同步,实现<1ns的跨节点时钟对齐

四、关键技术优化:从硬件到算法的垂直整合

4.1 算法层面的硬件亲和性优化

算子融合(Operator Fusion):

将STFT中的"加窗-FFT-取模"三个操作融合为单个CUDA Kernel,减少全局内存访问次数,降低延迟30%。

权重量化与剪枝:

-

使用NVIDIA TensorRT对威胁识别模型进行INT8量化,在A6000上推理延迟从8ms降至2ms,精度损失<1%

-

采用结构化剪枝,使模型适配GPU的Tensor Core计算模式,提升4倍吞吐

内存池化(Memory Pooling):

预先分配大容量显存池,避免运行时malloc/free的开销,消除内存碎片导致的延迟抖动。

4.2 系统级低延迟调优

CPU亲和性绑定:

使用

taskset或numactl将中断处理线程(IRQ)与实时计算线程绑定至不同NUMA节点,避免缓存失效。

禁用CPU频率调节:

在BIOS中关闭SpeedStep/Turbo Boost动态调频,锁定全核最高频率,消除频率切换导致的延迟尖峰(Latency Spike)。

内核旁路(Kernel Bypass):

使用DPDK(Data Plane Development Kit)处理网络数据包,绕过Linux内核协议栈,将网络延迟从毫秒级降至微秒级。

结语:构建电磁频谱优势的"数字底座"

雷达干扰决策模型的智能化演进,本质上是一场"算法复杂度"与"硬件实时性"的赛跑。当深度学习模型拥有数亿参数,当宽带接收机的数据流冲破10GB/s大关,当电子对抗要求亚毫秒级响应,普通的商用计算平台已触及物理极限。

UltraLAB深刻理解国防与科研领域对"确定性算力"的极致追求。我们的雷达干扰决策工作站不是简单的硬件堆砌,而是基于实时信号处理理论与异构计算架构的系统性工程:从FPGA的前端预处理,到GPU的并行推理,再到NVMe的高速记录,每一级都针对雷达信号的实时特征进行深度优化。

无论是需要验证新型认知干扰算法的实验室环境,还是要求严苛可靠的外场机动平台,UltraLAB都能提供"零丢帧、低抖动、高吞吐"的硬件底座。在电磁频谱这一无形战场上,让我们用坚实的算力基础设施,为您的智能决策算法争取那关键的毫秒级优势——因为在那毫秒之间,胜负已分。

关于UltraLAB实时信号处理解决方案

UltraLAB专注于高性能实时计算系统的研发与定制,服务领域涵盖雷达信号处理、电子对抗、软件定义无线电(SDR)、智能通信等。我们提供从边缘计算节点到数据中心集群的全谱系硬件方案,支持FPGA、GPU、CPU的深度协同优化,并提供实时Linux内核调优、CUDA并行优化、低延迟网络配置等专业服务。