新型宽带相控阵天线技术解析:雷达、通信与防御一体化设计的算力革命

时间:2026-03-25 22:31:41

来源:UltraLAB图形工作站方案网站

人气:38

作者:管理员

——从CapLink阵列看电磁仿真与信号处理的硬件极限挑战

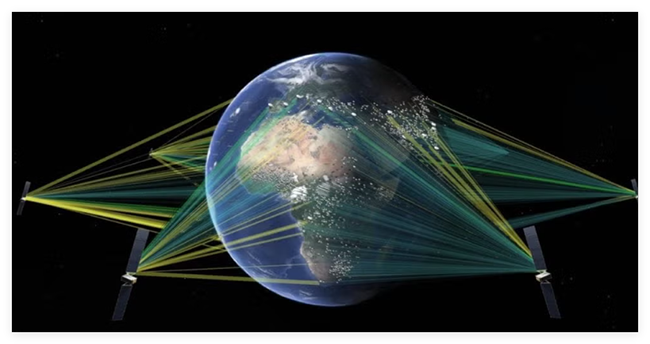

在国防信息化与商业航天双重驱动下,相控阵天线技术正经历从"专用分立"向"通用一体化"的范式转变。Assured Space公司最新推出的CapLink阵列天线,通过容性偶极子单元与软件定义无线电(SDR)架构的深度融合,实现了雷达探测、卫星通信与导弹防御三大功能的高度集成。这一技术突破背后,是电磁仿真算法、阵列信号处理与实时波束赋形计算对硬件算力的极致挑战。

一、核心技术架构解析

1. 容性偶极子单元:宽频带设计的电磁基础

CapLink阵列摒弃了传统窄带谐振单元,采用专有容性偶极子结构,通过电容性加载实现单元尺寸的电气小型化与宽带阻抗匹配。该技术的关键在于:

-

宽带阻抗匹配网络:通过容性耦合扩展工作带宽(通常覆盖S/C/X/Ku多频段)

-

可控单元间耦合:利用单元间的容性耦合特性优化阵列在宽角扫描时的有源驻波比

-

双极化分集:集成正交极化端口,支持极化分集接收与自适应极化抗干扰

2. 软件定义相控阵(SDPA)架构

CapLink的核心竞争力在于其软件定义无线电内核,实现了"硬件通用化+软件可重构":

-

数字化波束形成(DBF):阵列后端采用高速ADC/DAC,将模拟信号尽早数字化

-

多波形并发生成:通过FPGA/DSP实时生成雷达探测波形、通信调制波形与电子对抗波形

-

自适应波束调度:基于实时威胁评估动态分配阵列资源,实现多任务时分/频分复用

3. 大角度扫描补偿算法

传统相控阵在偏离法线方向扫描时会出现:

-

单元方向图增益下降(cos(θ)效应)

-

有源阻抗失配导致反射功率增加

-

波束宽度展宽与旁瓣电平升高

CapLink通过单元间可控耦合技术与子阵级相位优化算法,在±60°甚至更大扫描角范围内保持低旁瓣(通常<-30dB)与高增益,满足导弹防御系统对来袭目标的全程跟踪需求。

二、核心算法与计算特点

1. 全波电磁仿真算法(设计阶段)

相控阵天线设计涉及复杂的多尺度电磁问题,需采用分层级仿真策略:

| 仿真层级 | 算法类型 | 计算复杂度 | 硬件瓶颈 |

|---|---|---|---|

| 单元级设计 | FEM/FDTD | 网格数10⁶-10⁸ | 内存容量、单核频率 |

| 阵列级分析 | MoM/PO混合 | 未知量10⁴-10⁶ | 多核并行、高速互联 |

| 系统级场景 | 射线追踪/SBR | 弹跳次数10⁵+ | GPU加速、显存带宽 |

关键计算特征:

-

全波分析:对容性偶极子进行精确建模需采用时域有限差分(FDTD)或有限元法(FEM),计算资源随电尺寸呈O(n³)增长

-

周期结构分析:利用Floquet定理将无限阵列简化为单胞仿真,采用本征模求解器加速分析

-

互耦矩阵计算:大型阵列的互耦矩阵维度可达(N×N),需采用快速多极子(FMM)或自适应交叉近似(ACA)算法降低复杂度

2. 实时数字波束形成算法(运行阶段)

CapLink阵列在运行时的信号处理链包括:

(1)通道校准与误差补偿

-

幅相误差估计:基于内部校准信号或外部信标,采用最小二乘(LS)或特征子空间法估计各通道的幅相误差

-

温度漂移补偿:实时监测T/R组件温度,通过查找表或自适应算法补偿相位漂移

(2)自适应波束赋形

-

MVDR(最小方差无失真响应)算法:w=aH(θ0)Rnn−1a(θ0)Rnn−1a(θ0)

-

需要实时估计干扰协方差矩阵Rnn (维度=阵元数×阵元数)

-

涉及大规模矩阵求逆,计算复杂度O(N³)

-

-

子空间投影算法:利用特征分解分离信号子空间与噪声子空间,降低计算负担

(3)多目标跟踪与波形调度

-

Kalman滤波/粒子滤波:对多批次目标进行航迹关联与预测

-

凸优化波形设计:在满足距离分辨率、多普勒容忍度约束下优化波形自相关函数

3. 计算瓶颈分析

| 计算环节 | 计算密集型操作 | 精度要求 | 实时性要求 |

|---|---|---|---|

| 电磁仿真 | 大型稀疏矩阵求解 | 双精度浮点 | 离线(小时级) |

| DOA估计 | 空间谱搜索/特征分解 | 单精度浮点 | 准实时(秒级) |

| 波束形成 | 矩阵-向量乘法 | 定点/半精度 | 硬实时(微秒级) |

| 信号检测 | FFT/匹配滤波 | 定点 | 硬实时(纳秒级) |

三、应用场景与系统配置推荐

基于CapLink技术的典型应用场景对算力的差异化需求:

场景1:雷达信号处理与威胁模拟

技术需求:多目标跟踪、杂波抑制、ISAR成像

算法负载:

算法负载:

-

距离-多普勒处理(二维FFT,点数4096×4096)

-

空时自适应处理(STAP,空时维数1024×128)

-

逆合成孔径雷达(ISAR)成像(超分辨算法)

UltraLAB工作站配置推荐:

| 组件 | 配置规格 | 选型依据 |

|---|---|---|

| CPU | Intel Xeon 698X (86核/172线程) 或 AMD Ryzen Threadripper PRO 7995WX (96核) | 大规模并行矩阵运算,高内存带宽需求 |

| 内存 | 512GB DDR5-4800 ECC (8通道) | 存储大型协方差矩阵与原始回波数据 |

| GPU加速 | 2× NVIDIA RTX 4090 48GB或 RTX PRO 6000 (96GB) | CUDA加速STAP处理、CNN目标识别 |

| 存储 | 8TB NVMe SSD (读取速度>7GB/s) + 32TB RAID5 | 高速数据记录与多帧回波存储 |

| IO扩展 | 高速DAQ卡 (采样率≥1GS/s,分辨率≥14bit) | 直连阵列中频信号采集 |

场景2:卫星通信链路仿真与波形验证

技术需求:宽带调制解调、信道编译码、多普勒补偿

算法负载:

算法负载:

-

LDPC/Polar码编解码( belief propagation迭代)

-

宽带OFDM处理(子载波数4096,带宽500MHz)

-

自适应均衡与预失真

UltraLAB工作站配置推荐:

| 组件 | 配置规格 | 选型依据 |

|---|---|---|

| CPU | Intel Core i9-14900K 或 Xeon W7-3465X (28核) | 高主频要求,单核性能优先 |

| FPGA加速卡 | Xilinx Alveo U280 或 Intel Stratix 10 MX | 硬实时LDPC编解码、数字下变频 |

| 内存 | 256GB DDR5-5600 | 存储长码块与帧缓存 |

| 网络 | 100GbE网卡(如Mellanox ConnectX-6) | 高速IQ数据流传输 |

场景3:一体化阵列电磁设计仿真

技术需求:全阵列辐射特性优化、热-电耦合分析、安装平台效应

算法负载:

算法负载:

-

全波电磁仿真(Ansys HFSS/CST Studio Suite)

-

多物理场耦合(电磁-热-结构)

-

平台载体(飞机/舰船)上的天线布局分析

UltraLAB工作站配置推荐:

| 组件 | 配置规格 | 选型依据 |

|---|---|---|

| CPU | 2× AMD EPYC 9654 (96核/192线程×2) | 频域求解器高度并行化 |

| 内存 | 1TB-2TB DDR5-4800 | HFSS大规模矩阵求解内存需求 |

| 存储 | 15TB NVMe SSD (企业级) | 网格文件与场分布数据高速读写 |

| GPU | NVIDIA RTX 6000 Ada (48GB显存) | 加速时域求解与后处理可视化 |

四、关键技术实现路径

对于从事相控阵研发的科研团队,建议分阶段构建算力平台:

阶段1:算法验证(单节点高性能工作站)

-

重点:单核性能+大内存

-

配置:UltraLAB GT430P系列,Xeon W-3400系列,512GB内存

-

预算:15-25万元

阶段2:系统仿真(多节点集群)

-

重点:高速网络互联(InfiniBand 100Gbps)

-

配置:4-8节点集群,每节点64核+256GB内存

-

预算:80-150万元

阶段3:实时原型验证(异构计算平台)

-

重点:FPGA+GPU异构加速

-

配置:集成高速DAC/ADC的PXIE机箱+UltraLAB GPU工作站

-

预算:50-100万元

结语

CapLink阵列代表了相控阵技术从"硬件专用"向"软件定义"演进的重要方向。这一演进不仅改变了射频前端的架构设计,更对后端信号处理的算力提出了前所未有的挑战——从离线电磁仿真的大内存需求,到实时波束形成的纳秒级延迟约束,每一个环节都需要针对性的硬件优化。

对于国内从事雷达、卫星通信与电子对抗研究的科研单位而言,构建与算法迭代速度相匹配的算力基础设施,将成为缩短研发周期、提升系统性能的关键竞争要素。

如需针对具体仿真软件(如Ansys HFSS、CST、ADS或MATLAB Phased Array System Toolbox)的硬件配置细化方案,欢迎提供详细需求,我们将为您定制UltraLAB图形工作站/服务器配置清单。

UltraLAB图形工作站供货商:

西安坤隆计算机科技有限公司

国内知名高端定制图形工作站厂家

业务电话:400-705-6800

咨询微信号:xasun001